## **General Description**

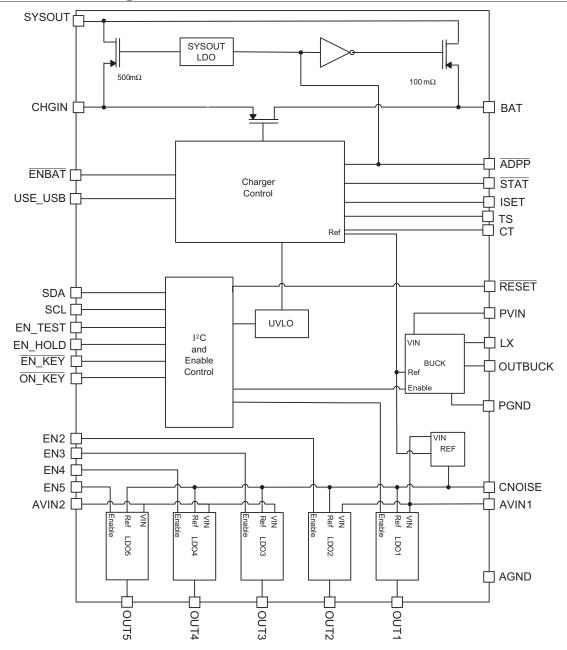

The AAT2601 is a member of AnalogicTech's Total Power Management IC<sup>TM</sup> (TPMIC<sup>TM</sup>) product family. It contains a single-cell Lithium Ion/Polymer battery charger, a fully integrated step-down converter and 5 low dropout (LDO) regulators. The device also includes 2 load switches for dynamic power path/sleep mode operation, making it ideal for small handheld portable GSM or CDMA mobile telephones.

The battery charger is a complete thermally regulated constant current/constant voltage linear charger. It includes an integrated pass device, reverse blocking protection, high accuracy current and voltage regulation, charge status, and charge termination. The charging current, charge termination current, and recharge voltage are programmable with an external resistor and/or by a standard I<sup>2</sup>C interface.

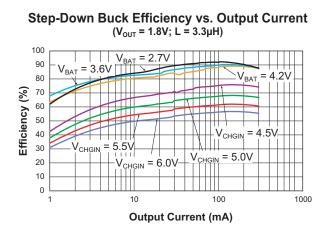

The step-down DC/DC converter is integrated with internal compensation and operates at a switching frequency of 1.5MHz, thus minimizing the size of external components while keeping switching losses low and efficiency greater than 95%. All LDO output voltages are programmable using the I<sup>2</sup>C interface.

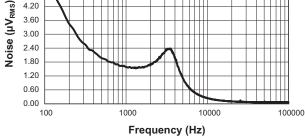

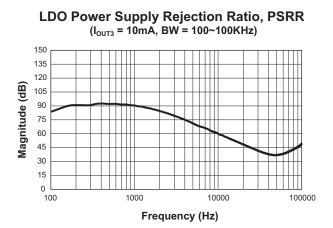

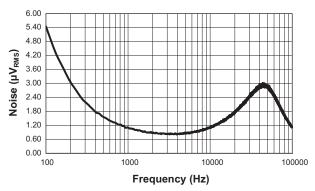

The five LDOs offer 60dB power supply rejection ratio (PSRR) and low noise operation making them suitable for powering noise-sensitive loads.

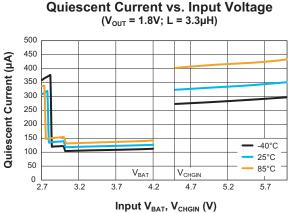

All six voltage regulators operate with low quiescent current. The total no load current when the step-down converter and 2 LDOs are enabled is only  $170\mu$ A.

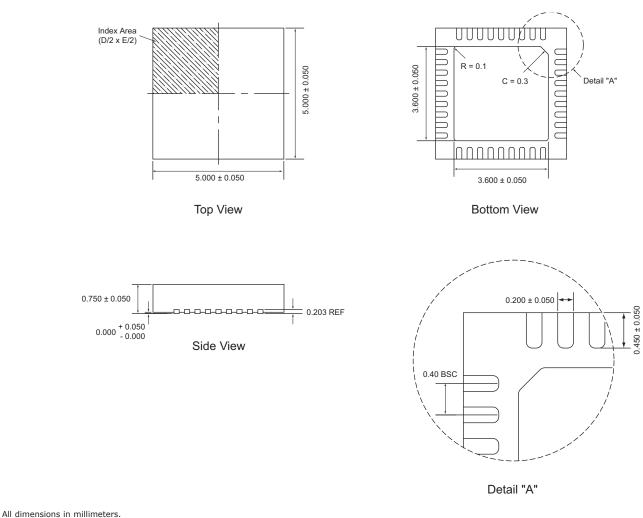

The AAT2601 is available in a thermally enhanced low profile 5x5x0.8mm 36-pin TQFN package.

#### Features

- Voltage Regulator  $V_{IN}$  Range: 4.5V to 6V

- Complete Power Integration

- Integrated Load Switches to Power Converters from AC Adapter or Battery Automatically

- Low Standby Current

- 170µA (typ) w/ Buck (Core), LDO1 (PowerDigital), and LDO2 (PowerAnalog) Active, No Load

- One Step-Down Buck Converter (Core)

- 1.8V, 300mA Output

- 1.5MHz Switching Frequency

- Fast Turn-On Time (120µs typ)

- Five LDOs Programmable with I<sup>2</sup>C

- LDO1: 3.0V, 300mA (PowerDigital)

- LDO2: 3.0V, 150mA (PowerAnalog or PLL)

- LDO3: 3.0V, 150mA (TCXO)

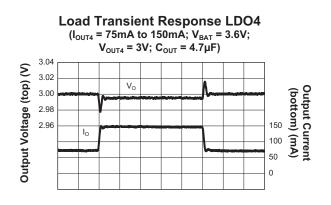

- LDO4: 3.0V, 150mA (TX)

- LDO5: 3.0V, 150mA (RX)

- PSRR: 60dB@10kHz

- Noise: 50µVrms for LDO3, LDO4, and LDO5

- One Battery Charger

- Digitized Thermal Regulation

- Charge Current Programming up to 1.4A

- Charge Current Termination Programming

- Automatic Trickle Charge for Battery Preconditioning (2.8V Cutoff)

- Adapter OK (ADPP) and Reset (RESET) Timer Outputs

- Separate Enable Pins for Supply Outputs

- Over-Current Protection

- Over-Temperature Protection

- 5x5mm TQFN55-36 Package

## **Applications**

- Digital Cameras

- GSM or CDMA Cellular Phones

- Handheld Instruments

- PDAs and Handheld Computers

- Portable Media Players

# **AAT260I**

## **Total Power Solution for Portable Applications**

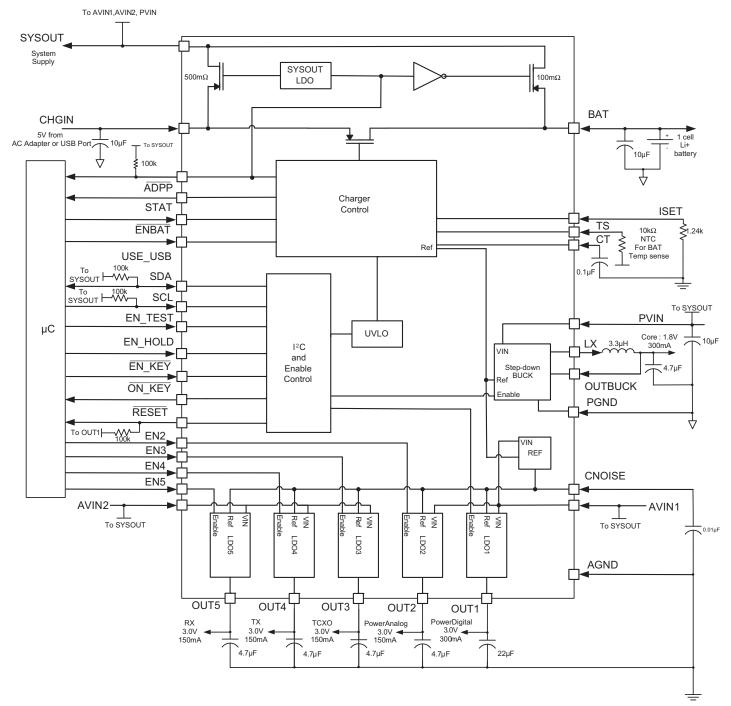

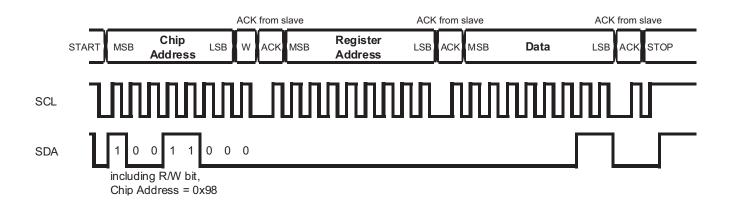

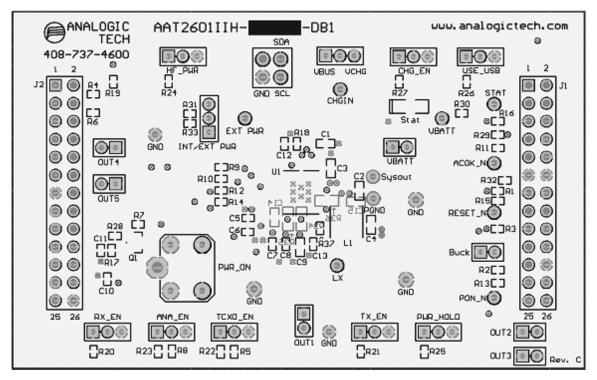

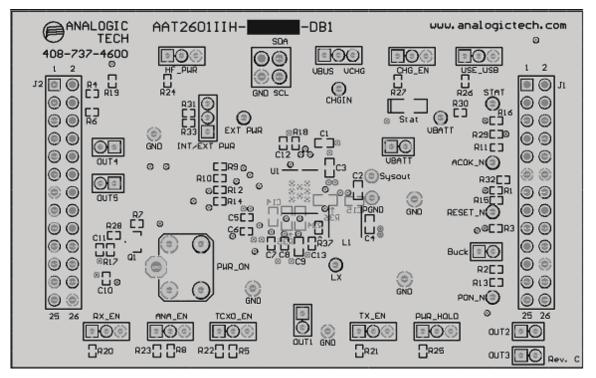

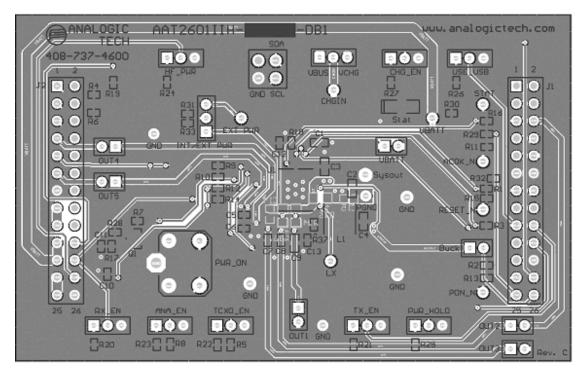

## **Typical Application**

## Total Power Solution for Portable Applications

## **Pin Descriptions**

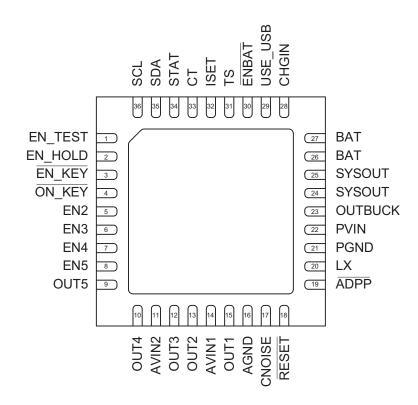

| Pin #  | Symbol  | Function                                                                                                                                                                                                                                                                                  |  |  |  |  |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1      | EN_TEST | Similar to EN_HOLD but intended for use with the automatic tester or as a hands free enable input pin indi-<br>cating hands free phone operation with a headset. It is also internally pulled to GND when floating.                                                                       |  |  |  |  |

| 2      | EN_HOLD | Enable for the system. EN_HOLD must be held high by the processor to maintain core power. It is inter-<br>nally pulled to GND when floating.                                                                                                                                              |  |  |  |  |

| 3      | EN_KEY  | Enable for the system. An internal pull-up resistor keeps the pin pulled up to an internal supply to keep the system off when there is no CHGIN input. Connect a normally-open pushbutton switch from this pin to GND. There is an internal 300ms debounce delay circuit to filter noise. |  |  |  |  |

| 4      | ON_KEY  |                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 5      | EN2     | Enable for LDO2 (PowerAnalog or PLL). (Internally pulled low when floating)                                                                                                                                                                                                               |  |  |  |  |

| 6      | EN3     | Enable for LDO3 (TCXO). (Internally pulled low when floating)                                                                                                                                                                                                                             |  |  |  |  |

| 7      | EN4     | Enable for LDO4 (TX) (Internally pulled low when floating)                                                                                                                                                                                                                                |  |  |  |  |

| 8      | EN5     | Enable for LDO5 (RX) (Internally pulled low when floating)                                                                                                                                                                                                                                |  |  |  |  |

| 9      | OUT5    | Output for LDO5 (RX) (when shut down, pulled down with $10k\Omega$ )                                                                                                                                                                                                                      |  |  |  |  |

| 10     | OUT4    | Output for LDO4 (TX) (when shut down, pulled down with $10k\Omega$ )                                                                                                                                                                                                                      |  |  |  |  |

| 11     | AVIN2   | Analog voltage input. Must be tied to SYSOUT on the PCB.                                                                                                                                                                                                                                  |  |  |  |  |

| 12     | OUT3    | Output for LDO3 (TCXO)                                                                                                                                                                                                                                                                    |  |  |  |  |

| 13     | OUT2    | Output for LDO2 (PowerAnalog)                                                                                                                                                                                                                                                             |  |  |  |  |

| 14     | AVIN1   | Analog voltage input. Must be tied to SYSOUT on the PCB.                                                                                                                                                                                                                                  |  |  |  |  |

| 15     | OUT1    | Output for LDO1 (PowerDigital)                                                                                                                                                                                                                                                            |  |  |  |  |

| 16     | AGND    | Signal ground                                                                                                                                                                                                                                                                             |  |  |  |  |

| 17     | CNOISE  | Noise Bypass pin for the internal reference voltage. Connect a 0.01µF capacitor to AGND.                                                                                                                                                                                                  |  |  |  |  |

| 18     | RESET   | RESET is the open drain output of a 50ms reset timer. RESET is released after the 50ms timer times out.<br>RESET is active low and is held low during shutdown. RESET should be tied to a 10K or larger pullup to OUTBUCK.                                                                |  |  |  |  |

| 19     | ADPP    | Open Drain output. Will pull low when $V_{CHGIN} > 4.5V$ . When this happens, depending on the status of the USE_USB pin, the charge current will be reset to the default values (see Battery Charger and I <sup>2</sup> C Serial Interface and Programmability section)                  |  |  |  |  |

| 20     | LX      | Step-down Buck converter (Core) switching node. Connect an inductor between this pin and the output.                                                                                                                                                                                      |  |  |  |  |

| 21     | PGND    | Power Ground for step-down Buck converter (Core)                                                                                                                                                                                                                                          |  |  |  |  |

| 22     | PVIN    | Input power for step-down Buck converter (Core). Must be tied to SYSOUT.                                                                                                                                                                                                                  |  |  |  |  |

| 23     | OUTBUCK | Feedback input for the step-down Buck converter (Core)                                                                                                                                                                                                                                    |  |  |  |  |

| 24, 25 | SYSOUT  | System Power output. Connect to the input voltage pins PIN, AVIN1/2 for the step-down converter and LDOs and other external supply requirements.                                                                                                                                          |  |  |  |  |

| 26, 27 | BAT     | Connect to a Lithium Ion battery.                                                                                                                                                                                                                                                         |  |  |  |  |

| 28     | CHGIN   | Power input from either external adapter or USB port.                                                                                                                                                                                                                                     |  |  |  |  |

| 29     | USE_USB | When pulled high, fast charge current is set to 100mA regardless of the resistor value present on the ISET pin. Additionally, the CHGIN-SYSOUT LDO will be disabled and the BAT-SYSOUT load switch will be enabled.                                                                       |  |  |  |  |

| 30     | ENBAT   | Active low enable for the battery charger (Internally pulled low when floating)                                                                                                                                                                                                           |  |  |  |  |

| 31     | TS      | Battery Temperature Sense pin with $75\mu A$ output current. Connect the battery's NTC resistor to this pin and ground.                                                                                                                                                                   |  |  |  |  |

| 32     | ISET    | Charge current programming input pin (Tie a 1k to GND for maximum fast charge current). Can be used to monitor charge current.                                                                                                                                                            |  |  |  |  |

| 33     | СТ      | Charger Safety Timer Pin. A $0.1\mu$ F ceramic capacitor should be connected between this pin and GND. Connect directly to GND to disable the timer function.                                                                                                                             |  |  |  |  |

| 34     | STAT    | Battery charging status pin output. Connected internally between GND and OUT1 (PowerDigital). Used to monitor battery charge status.                                                                                                                                                      |  |  |  |  |

| 35     | SDA     | I <sup>2</sup> C serial data pin, open drain; requires a pullup resistor.                                                                                                                                                                                                                 |  |  |  |  |

| 36     | SCL     | I <sup>2</sup> C serial clock pin, open drain; requires a pullup resistor.                                                                                                                                                                                                                |  |  |  |  |

| EP     | EP      | The exposed thermal pad (EP) must be connected to board ground plane and pins 16 and 21. The ground plane should include a large exposed copper pad under the package for thermal dissipation (see package outline).                                                                      |  |  |  |  |

## **Pin Configuration**

TQFN55-36 (Top View)

## **Total Power Solution for Portable Applications**

## Absolute Maximum Ratings<sup>1</sup>

$T_A = 25^{\circ}C$  unless otherwise noted.

| Symbol               | Description                                      | Value                 | Units |

|----------------------|--------------------------------------------------|-----------------------|-------|

| V <sub>IN</sub>      | Input Voltage, CHGIN, BAT                        | -0.3 to 6.5           | V     |

| Power and logic pins | Maximum Rating                                   | V <sub>IN</sub> + 0.3 | V     |

| T <sub>J</sub>       | Operating Junction Temperature Range             | -40 to 85             | °C    |

| T <sub>s</sub>       | Storage Temperature Range                        | -65 to 150            | °C    |

| T <sub>LEAD</sub>    | Maximum Soldering Temperature (at leads, 10 sec) | 300                   | °C    |

## **Recommended Operating Conditions<sup>2</sup>**

| Symbol          | Description               | Value | Units |

|-----------------|---------------------------|-------|-------|

| θ <sub>JA</sub> | Thermal Resistance        | 25    | °C/W  |

| P <sub>D</sub>  | Maximum Power Dissipation | 4     | W     |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>2.</sup> Thermal Resistance was measured with the AAT2601 device on the 4-layer FR4 evaluation board in a thermal oven. The amount of power dissipation which will cause the thermal shutdown to activate will depend on the ambient temperature and the PC board layout ability to dissipate the heat. See Figures 11-14.

# **AAT260I**

## **Total Power Solution for Portable Applications**

## **Electrical Characteristics**<sup>1</sup>

$V_{IN}$  = 5V,  $V_{BAT}$  = 3.6V, -40°C ≤  $T_A$  ≤ +85°C, unless noted otherwise. Typical values are  $T_A$  = 25°C.

| Symbol                                       | Description                                     | Conditions                                                                                                                                                           | Min   | Тур          | Max               | Units                   |

|----------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|-------------------|-------------------------|

| Power Sup                                    | ply                                             |                                                                                                                                                                      |       | I            |                   |                         |

| V <sub>IN</sub>                              | CHGIN Input Voltage                             |                                                                                                                                                                      | 4.5   |              | 6                 | V                       |

| Io                                           | Battery Standby Current                         | Buck, LDO1 + LDO2, no load                                                                                                                                           |       | 170          |                   | μA                      |

| I <sub>SHDN</sub>                            | Battery Shutdown Current                        | EN_TEST, EN_HOLD, EN2, EN3, EN4, EN5<br>= GND, EN_KEY floating                                                                                                       |       |              | 10.0              | μA                      |

|                                              | Under-Voltage Lockout for CHGIN                 | CHGIN rising<br>CHGIN falling                                                                                                                                        |       | 4.25<br>4.15 | 4.5               | V                       |

| UVLO                                         | Battery Under-Voltage Lockout                   | BAT rising                                                                                                                                                           |       | 2.6          |                   | V                       |

| -                                            |                                                 | BAT falling                                                                                                                                                          |       | 2.35         | _                 | V                       |

| I <sub>BAT</sub>                             | Leakage Current from BAT Pin                    | $V_{BAT} = 4V, V_{CHGIN} = 0V$                                                                                                                                       |       | 2            | 5                 | μA                      |

| Startup Ti                                   |                                                 |                                                                                                                                                                      | 1     | 1            | 1                 | 1                       |

| RESET                                        | Reset Timer                                     | Initiated when $OUT1 = 90\%$ of final value                                                                                                                          | 35    |              |                   | ms                      |

| Charger V                                    | oltage Regulation                               |                                                                                                                                                                      |       |              |                   |                         |

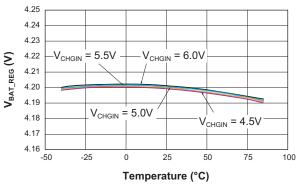

| $V_{BAT\_REG}$                               | Output Charge Voltage Regulation                | $0^{\circ}C \leq T_{A} \leq +70^{\circ}C$                                                                                                                            | 4.158 | 4.200        | 4.242             | V                       |

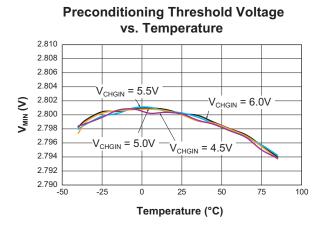

| V <sub>MIN</sub>                             | Preconditioning Voltage Threshold               | (No trickle charge option available)                                                                                                                                 | 2.6   | 2.8          | 3.0               | V                       |

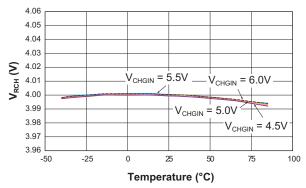

|                                              |                                                 | I <sup>2</sup> C Recharge Code = 00 (default)                                                                                                                        |       | 4.00         |                   | V                       |

| N/                                           | Battery Recharge Voltage Threshold              | $I^2C$ Recharge Code = 01                                                                                                                                            |       | 4.05         |                   | V                       |

| $V_{RCH}$                                    | Battery Recharge Voltage Threshold              | $I^2C$ Recharge Code = 10                                                                                                                                            |       | 4.10         |                   | V                       |

|                                              |                                                 | I <sup>2</sup> C Recharge Code = 11                                                                                                                                  |       | 4.15         |                   | V                       |

| Charger C                                    | urrent Regulation                               |                                                                                                                                                                      |       |              |                   |                         |

| I <sub>CH CC</sub>                           | Constant-Current Mode Charge Current            | $ \begin{array}{l} R_{ISET} = 1.24 k \; (for \; 0.8 A), \; USE\_USB = Low, \\ I^2 C \; ISET \; code = 000, \; V_{BAT} = 3.6 V, \; V_{CHGIN} \\ = 5.0 V \end{array} $ | 720   | 800          | 880               | mA                      |

| ch_cc                                        |                                                 | USE_USB = High, I <sup>2</sup> C ISET Code = 000,<br>$V_{BAT} = 3.6V$                                                                                                | 85    | 100          | 115               |                         |

| KI_SET                                       | Charge Current Set Factor: $I_{CH_CC}/I_{ISET}$ | Constant Current Mode, $V_{BAT} = 3.6V$                                                                                                                              |       | 800          |                   | mA                      |

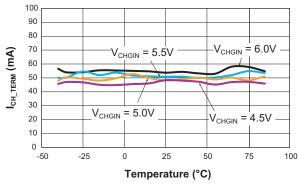

| $I_{CH_PRE}$                                 | Preconditioning Charge Current                  | $R_{ISET} = 1.24 k\Omega$ , USE_USB = Low                                                                                                                            |       | 12           |                   | %<br>І <sub>сн_сс</sub> |

| <u>-</u>                                     |                                                 | I <sup>2</sup> C ISET Code = 000, USE_USB = High                                                                                                                     |       | 50           |                   | mA                      |

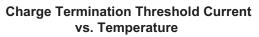

|                                              |                                                 | I <sup>2</sup> C Term Code = 00 (default)                                                                                                                            |       | 5            |                   |                         |

|                                              |                                                 | $I^2C$ Term Code = 01                                                                                                                                                |       | 10           |                   | %                       |

| $I_{CH\_TERM}$                               | Charge Termination Threshold Current            | $I^2C$ Term Code = 10                                                                                                                                                |       | 15           |                   | I <sub>CH CC</sub>      |

|                                              |                                                 | I <sup>2</sup> C Term Code = 11                                                                                                                                      |       | 20           |                   |                         |

| Charging I                                   | Devices                                         |                                                                                                                                                                      |       |              |                   |                         |

| R <sub>DS(ON)</sub>                          | Charging Transistor ON Resistance               | $V_{IN} = 5V$                                                                                                                                                        |       | 0.6          | 0.9               | Ω                       |

|                                              | rol / Protection                                | 214 -                                                                                                                                                                |       |              |                   |                         |

| V <sub>EN_HOLD</sub> ,                       | Input High Threshold                            |                                                                                                                                                                      | 1.4   |              |                   | V                       |

| V <sub>en_key,</sub><br>V <sub>en_test</sub> | Input Low Threshold                             |                                                                                                                                                                      |       |              | 0.4               | V                       |

| VADPP                                        | Output Low Voltage                              | Pin Sinks 4mA                                                                                                                                                        |       |              | 0.4               | V                       |

| IADPP                                        | Output Pin Current Sink Capability              |                                                                                                                                                                      |       |              | 8                 | mA                      |

| V <sub>STAT</sub>                            | Output High Voltage                             |                                                                                                                                                                      |       |              | V <sub>OUT1</sub> | V                       |

| I <sub>STAT</sub>                            | Output Pin Current Source Capability            |                                                                                                                                                                      |       |              | 1.5               | mA                      |

| V <sub>OVP</sub>                             | Over-Voltage Protection Threshold               |                                                                                                                                                                      |       | 4.3          | -                 | V                       |

1. Specification over the -40°C to +85°C operating temperature range is assured by design, characterization and correlation with statistical process controls.

## **Total Power Solution for Portable Applications**

## **Electrical Characteristics**<sup>1</sup>

$V_{IN}$  = 5V,  $V_{BAT}$  = 3.6V, -40°C ≤  $T_A$  ≤ +85°C, unless noted otherwise. Typical values are  $T_A$  = 25°C.

| Symbol                                    | Description                                  | Conditions                                                                    | Min  | Тур               | Max  | Units            |

|-------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------|------|-------------------|------|------------------|

| Logic Control / I                         | Protection (continued)                       |                                                                               |      |                   |      |                  |

| V <sub>OCP</sub>                          | Over Current Protection Threshold            |                                                                               |      | 105               |      | %V <sub>cs</sub> |

| T <sub>c</sub>                            | Constant Current Mode Time Out               |                                                                               |      | 3                 |      | Hours            |

| Τ <sub>κ</sub>                            | Trickle Charge Time Out                      | $C_{CT} = 100 nF, V_{CHGIN} = 5V$                                             |      | T <sub>c</sub> /8 |      | Hours            |

| Tv                                        | Constant Voltage Mode Time Out               |                                                                               |      | 3                 |      | Hours            |

| I <sub>TS</sub>                           | Current Source from TS Pin                   |                                                                               | 71   | 75                | 79   | μA               |

| TC                                        |                                              | Falling Threshold                                                             | 318  | 331               | 346  |                  |

| TS <sub>1</sub>                           | TS Hot Temperature Fault                     | Hysteresis                                                                    |      | 25                |      | mV               |

| тс                                        | TC Cold Tommorphyse Foult                    | Rising Threshold                                                              | 2.30 | 2.39              | 2.48 | V                |

| TS <sub>2</sub>                           | TS Cold Temperature Fault                    | Hysteresis                                                                    |      | 25                |      | mV               |

| T <sub>LOOP_IN</sub>                      | Thermal Loop Entering Threshold              |                                                                               |      | 115               |      | °C               |

| T <sub>LOOP_OUT</sub>                     | Thermal Loop Exiting Threshold               |                                                                               |      | 85                |      | °C               |

| T <sub>REG</sub>                          | Thermal Loop Regulation                      |                                                                               |      | 100               |      | °C               |

| Load Switches /                           | ' SYSOUT LDO                                 |                                                                               |      |                   |      |                  |

| R <sub>DS(ON),BAT-SYSOUT</sub>            | On-Resistance of BAT-SYSOUT<br>Load Switch   | V <sub>BAT</sub> = 3.6V                                                       |      | 100               | 150  | mΩ               |

| R <sub>DS(ON),CHGIN-SYSOUT</sub>          | On-Resistance of CHGIN-SYSOUT<br>Load Switch | $V_{CHGIN} = 4.5V$                                                            |      | 0.5               | 0.75 | Ω                |

|                                           | Sysout LDO Input Voltage Range               |                                                                               | 4.5  |                   |      | V                |

|                                           | Sysout LDO Output Voltage                    | $I_{SYSOUT} < 900 \text{mA}, V_{CHGIN} = 4.5 \text{V} \sim 6.0 \text{V}$      | 3.4  | 3.9               | 4.2  | V                |

| Step-Down Buck                            | Converter (Core)                             | ·                                                                             |      |                   |      |                  |

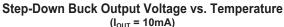

| VOUTBUCK                                  | Output Voltage Accuracy                      | $I_{OUTBUCK} = 0 \sim 300 \text{mA}; V_{IN} = 2.7 \text{V} \sim 5.5 \text{V}$ | 1.71 | 1.80              | 1.89 | V                |

| ILIMOUTBUCK                               | P-Channel Current Limit                      |                                                                               |      | 0.8               |      | Α                |

| R <sub>DS(ON)L</sub>                      | High Side Switch On-Resistance               |                                                                               |      | 0.8               |      | Ω                |

| R <sub>DS(ON)H</sub>                      | Low Side Switch On-Resistance                |                                                                               |      | 0.8               |      | Ω                |

| Fosc                                      | Oscillator Frequency                         | $T_A = 25^{\circ}C$                                                           |      | 1.5               |      | MHz              |

| Τ <sub>s</sub>                            | Start-Up Time                                | From Enable to Regulation; $C_{OUTBUCK} = 4.7 \mu F$ , $C_{NOISE} = On$       |      | 100               |      | μs               |

| LDO1 (PowerDig                            | gital)                                       |                                                                               |      |                   |      |                  |

| V <sub>OUT1</sub>                         | Output Voltage Accuracy                      | I <sub>OUT1</sub> = 0~300mA, V <sub>AVINx</sub> = 3.3V ~ 5.5V                 | -3   |                   | +3   | %                |

| I <sub>out1</sub>                         | Output Current                               |                                                                               | 300  |                   |      | mA               |

| $I_{LIM1}$                                | Output Current Limit                         |                                                                               |      | 1000              |      | mA               |

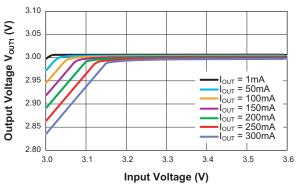

| V <sub>DO1</sub>                          | Dropout Voltage                              | I <sub>OUT1</sub> = 300mA                                                     |      | 150               | 300  | mV               |

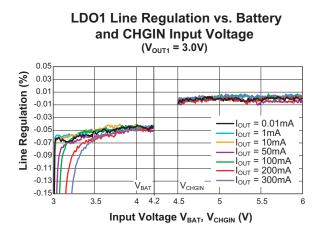

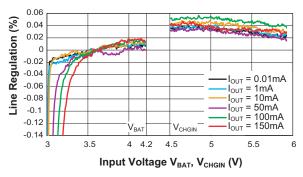

| $\Delta V_{OUT1}(V_{OUT1}\Delta V_{IN1})$ | Line Regulation                              | $I_{OUT1} = 100 \text{mA}, 3.3 \text{V} < V_{AVINx} < 5.5 \text{V}$           |      |                   | 0.07 | %/V              |

| ΔV <sub>OUT1</sub>                        | Load Regulation                              | $I_{OUT1} = 0.5 \text{mA} \sim 150 \text{mA}$                                 |      | 40                |      | mV               |

| PSRR                                      | Power Supply Rejection Ratio                 | $I_{OUT1} = 10$ mA, $C_{OUT1} = 22\mu$ F, 100Hz ~ 10KHz                       |      | 60                |      | dB               |

| Ts                                        | Start Up Time                                | From Enable to Regulation; $C_{OUT1} = 22\mu$ F, $C_{NOISE} = On$             |      | 175               |      | μs               |

1. Specification over the -40°C to +85°C operating temperature range is assured by design, characterization and correlation with statistical process controls.

**AAT260I**

## **Total Power Solution for Portable Applications**

## **Electrical Characteristics**<sup>1</sup>

$V_{IN}$  = 5V,  $V_{BAT}$  = 3.6V, -40°C ≤  $T_A$  ≤ +85°C, unless noted otherwise. Typical values are  $T_A$  = 25°C.

| Symbol                                                         | Description Conditions                         |                                                                                    | Min  | Тур  | Max  | Units |

|----------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------|------|------|------|-------|

| LDO2 (Pow                                                      | verAnalog)                                     |                                                                                    |      |      |      | I     |

| V <sub>OUT2</sub>                                              | Output Voltage Accuracy                        | I <sub>OUT2</sub> = 0 ~ 150mA, V <sub>AVINx</sub> : 3.3V ~ 5.5V                    | -3   |      | +3   | %     |

| I <sub>OUT2</sub>                                              | Output Current                                 |                                                                                    | 150  |      |      | mA    |

| $I_{LIM2}$                                                     | Output Current Limit                           |                                                                                    |      | 1000 |      | mA    |

| V <sub>DO2</sub>                                               | Dropout Voltage                                | $I_{OUT2} = 150 \text{mA}$                                                         |      | 150  |      | mV    |

| $\Delta V_{OUT2}/(V_{OUT2}\Delta V_{IN2})$                     | Line Regulation                                | $I_{OUT2} = 100 \text{mA}, 3.3 \text{V} < V_{\text{AVINx}} < 5.5 \text{V}$         |      |      | 0.07 | %/V   |

| $\Delta V_{OUT2}$                                              | Load Regulation                                | Load: 0.5mA~150mA                                                                  |      | 40   |      | mV    |

| PSRR                                                           | Power Supply Rejection Ratio                   | $I_{OUT2} = 10$ mA, $C_{OUT2} = 4.7\mu$ F, $10 \sim 10$ KHz                        |      | 60   |      | dB    |

| Ts                                                             | Start Up Time                                  | From Enable to Regulation; $C_{\text{OUT2}} = 4.7 \mu$ F, $C_{\text{NOISE}} = 0$ n |      | 65   |      | μs    |

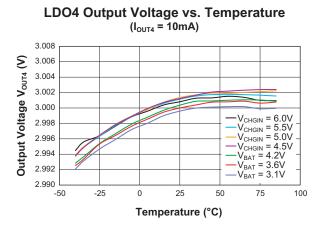

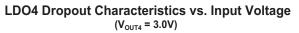

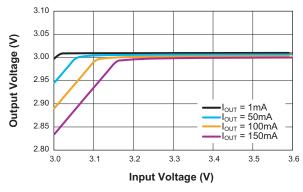

| LDO3 (TCX                                                      | O), LDO4 (TX) and LDO5 (RX)                    |                                                                                    |      |      |      |       |

| V <sub>OUTx</sub>                                              | Output Voltage Accuracy                        | $I_{OUTX} = 0 \sim 150 \text{mA}, V_{AVINx} = 3.3 \text{V} \sim 5.5 \text{V}$      | -3   |      | +3   | %     |

| I <sub>OUTx</sub>                                              | Output Current                                 |                                                                                    | 150  |      |      | mA    |

| $I_{\text{LIMx}}$                                              | Output Current Limit                           |                                                                                    |      | 1000 |      | mA    |

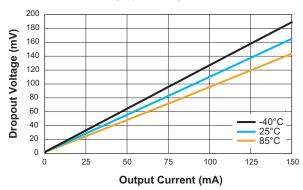

| V <sub>DOx</sub>                                               | Dropout Voltage                                | $I_{OUTX} = 150 \text{mA}$                                                         |      | 150  |      | mV    |

| ΔV <sub>OUTx</sub> /<br>(V <sub>OUTx</sub> ΔV <sub>INx</sub> ) | Line Regulation                                | $I_{OUTX} = 100 \text{mA}, 3.3 \text{V} < V_{AVINx} < 5.5 \text{V}$                |      |      | 0.07 | %/V   |

| ΔV <sub>OUTx</sub>                                             | Load Regulation                                | $I_{OUTX} = 0.5 \text{mA} \sim 150 \text{mA}$                                      |      | 40   |      | mV    |

| PSRR                                                           | Power Supply Rejection Ratio                   | $I_{OUTx} = 10 \text{mA}, C_{OUTx} = 4.7 \mu\text{F}, 10 \sim 10 \text{KHz}$       |      | 60   |      | dB    |

| e <sub>N</sub>                                                 | Output Noise Voltage                           | $I_{OUTX} = 10$ mA, Power BW: 10kHz ~ 100KHz                                       |      | 40   |      | μVrms |

| Ts                                                             | Start Up Time                                  | From Enable to Regulation; $C_{OUTX} = 4.7 \mu F$ , $C_{NOISE} = On$               |      | 65   |      | μs    |

| Logic Contr                                                    | ol                                             |                                                                                    |      | 1    |      |       |

| VIH                                                            | Enable Pin Logic High Level                    | For EN2, EN3, EN4 and EN5                                                          | 1.4  |      |      | V     |

| V <sub>IL</sub>                                                | Enable Pin Logic Low Level                     |                                                                                    |      |      | 0.4  | V     |

| Thermal                                                        | -                                              |                                                                                    |      |      |      |       |

| T <sub>SD</sub>                                                | Over Temperature Shutdown Threshold            |                                                                                    |      | 140  |      | °C    |

| T <sub>HYS</sub>                                               | Over Temperature Shutdown Hysteresis           |                                                                                    |      | 15   |      | °C    |

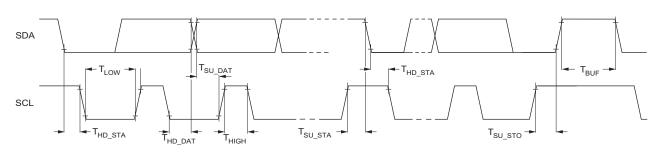

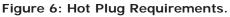

| SCL, SDA (I                                                    | I <sup>2</sup> C Interface)                    |                                                                                    |      |      |      |       |

| F <sub>SCL</sub>                                               | Clock Frequency                                |                                                                                    | 0    |      | 400  | KHz   |

| T <sub>LOW</sub>                                               | Clock Low Period                               |                                                                                    | 1.3  |      |      | μs    |

| T <sub>HIGH</sub>                                              | Clock High Period                              |                                                                                    | 0.6  |      |      | μs    |

| T <sub>HD_STA</sub>                                            | Hold Time START Condition                      |                                                                                    | 0.6  |      |      | μs    |

| $T_{SU}STA$                                                    | Setup Time for Repeat START                    |                                                                                    | 0.6  |      |      | μs    |

| $T_{SU_DTA}$                                                   | Data Setup Time                                |                                                                                    | 100  |      |      | ns    |

| T <sub>HD_DAT</sub>                                            | Data Hold Low                                  |                                                                                    | 0    |      | 0.9  | μs    |

| T <sub>SU_STO</sub>                                            | Setup Time for STOP Condition                  |                                                                                    | 0.6  |      |      | μs    |

| $T_{BUF}$                                                      | Bus Free Time Between STOP and START Condition |                                                                                    | 1.3  |      |      | μs    |

| V <sub>IL</sub>                                                | Input Threshold Low                            | $2.7V \leq V_{IN} \leq 5.5V$                                                       |      |      | 0.4  | V     |

| V <sub>IH</sub>                                                | Input Threshold High                           | $2.7V \leq V_{IN} \leq 5.5V$                                                       | 1.4  |      | -    | V     |

| I                                                              | Input Current                                  | 20                                                                                 | -1.0 |      | 1.0  | μA    |

| V <sub>OL</sub>                                                | Output Logic Low (SDA)                         | I <sub>PULLUP</sub> = 3mA                                                          |      | 1    | 0.4  | V     |

1. Specification over the -40°C to +85°C operating temperature range is assured by design, characterization and correlation with statistical process controls.

## Basic I<sup>2</sup>C Timing Diagram

**AAT2601**

## **Total Power Solution for Portable Applications**

## **Typical Characteristics—Charger**

## Recharge Voltage Threshold vs. Temperature (V<sub>RCH</sub> set to 4.0V)

# Output Charge Voltage Regulation vs. Temperature (End of Charge Voltage)

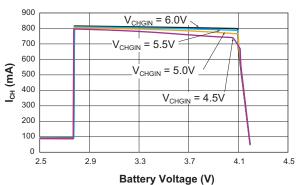

# Charging Current vs. Battery Voltage $(R_{ISET} = 1.24k\Omega)$

**AAT260I**

## **Total Power Solution for Portable Applications**

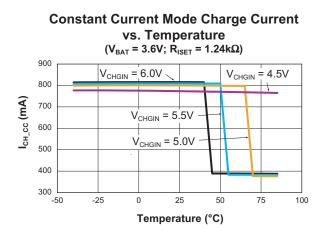

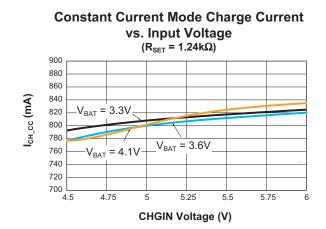

## Typical Characteristics—Charger (continued)

**AAT260**

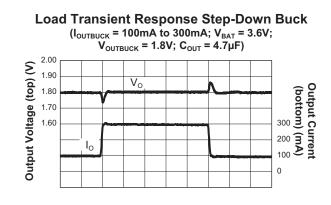

## **Typical Characteristics—Step-Down Buck Converter**

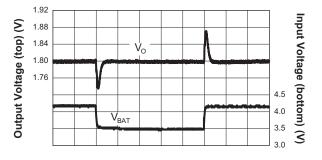

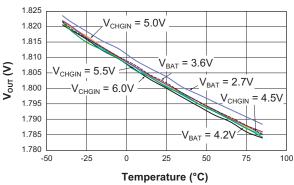

V<sub>BAT</sub> Line Transient Response Step-Down Buck  $(V_{BAT} = 3.5V \text{ to } 4.2V; I_{OUT} = 300\text{mA}; V_{OUT} = 1.8V; C_{OUT} = 4.7\mu\text{F})$

Time (100µs/div)

V<sub>CHGIN</sub> Line Transient Response Step-Down Buck (V<sub>CHGIN</sub> = 4.5V to 5.5V; I<sub>OUT</sub> = 300mA; V<sub>OUT</sub> = 1.8V; C<sub>OUT</sub> = 4.7 $\mu$ F)

Time (100µs/div)

(I<sub>OUT</sub> = 10mA)

## **Total Power Solution for Portable Applications**

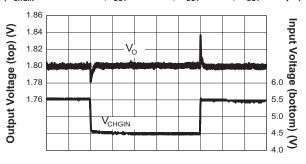

## Typical Characteristics—Step-Down Buck Converter (continued)

Time (100µs/div)

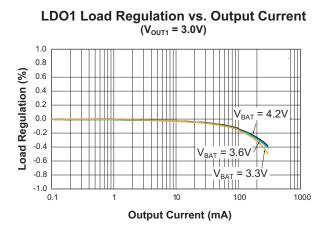

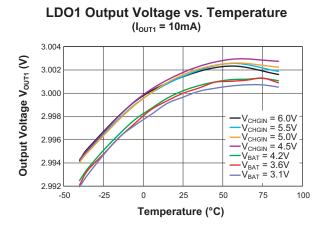

## **Typical Characteristics—LDO1**

LDO1 Dropout Characteristics vs. Input Voltage (V<sub>OUT1</sub> = 3.0V)

## **Total Power Solution for Portable Applications**

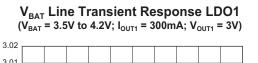

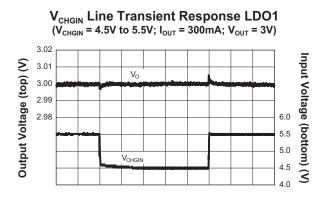

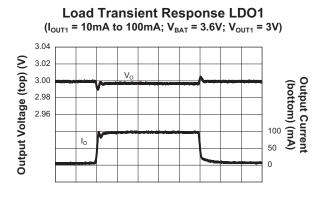

## Typical Characteristics—LDO1 (continued)

Time (100µs/div)

Time (100µs/div)

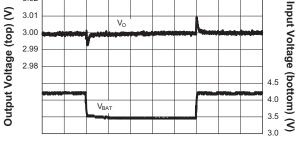

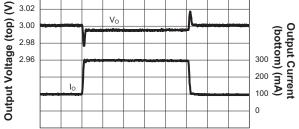

Load Transient Response LDO1 ( $I_{OUT1} = 100$ mA to 300mA;  $V_{BAT} = 3.6V$ ;  $V_{OUT1} = 3V$ ) 3.04 3.02 3.00  $V_0$   $V_0$  $V_0$

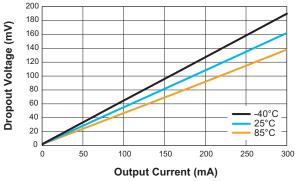

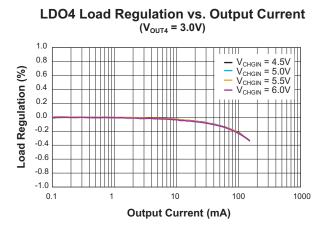

## **Typical Characteristics—LDO4**

LDO4 Dropout Voltage vs. Output Current (V<sub>0UT4</sub> = 3.0V)

## **Total Power Solution for Portable Applications**

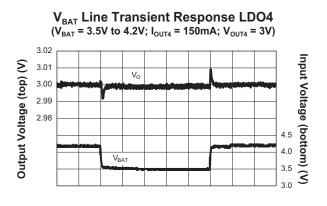

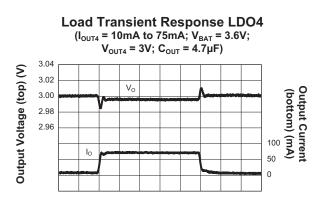

## Typical Characteristics—LDO4 (continued)

Time (100µs/div)

Time (100µs/div)

V<sub>CHGIN</sub> Line Transient Response LDO4  $(V_{CHGIN} = 4.5V \text{ to } 5.5V; I_{OUT4} = 150\text{ mA}; V_{OUT4} = 3V)$ 3.02 Input Voltage (bottom) (V) Output Voltage (top) (V) 3.01 Vo 3.00 2.99 6.0 2.98 5.5 5.0 VCHGIN 4.5 4.0

Time (100µs/div)

## **Typical Characteristics—General**

Time (50µs/div)

LDO Output Voltage Noise (I<sub>outs</sub> = 10mA, Power BW = 100~100KHz)

## Total Power Solution for Portable Applications

## **Functional Block Diagram**

## **Functional Description**

The AAT2601 is a complete power management solution. It seamlessly integrates an intelligent, stand-alone CC/ CV (Constant Current/Constant Voltage), linear-mode single-cell battery charger with one step-down Buck converter and five low-dropout (LDO) regulators to provide power from either a wall adapter or a single-cell Lithium Ion/Polymer battery. Internal load switches allow the LDO regulators and DC-DC converter to operate from the best available power source of either an AC wall adapter, USB port supply or battery.

If only the battery is available, then the voltage regulators and converter are powered directly from the battery through a  $100m\Omega$  load switch. (The charger is put into sleep mode and draws less than 1µA quiescent current.)

## **Total Power Solution for Portable Applications**

If the system is connected to a wall adapter, then the voltage converters are powered directly from the adapter through a 500m $\Omega$  load switch and the battery is disconnected from the voltage converter inputs. This allows the system to operate regardless of the charging state of the battery or with no battery.

#### System Output (SYSOUT)

Intelligent control of the integrated load switches is managed by the switch control circuitry to allow the Step-down converter and the LDOs to have the best available power source. When the CHGIN pin voltage is above 4.5V, the system automatically turns on and the power to the SYSOUT pin will be provided by either the CHGIN pin or the BAT pin. When the USE\_USB pin is low, the CHGIN provides power to SYSOUT through an internal LDO regulated to 3.9V. When the USE\_USB pin is high or if forced through use of an I<sup>2</sup>C command, the BAT pin is shorted to SYSOUT through a 100mohm switch. If a CHGIN voltage is not present and the system is enabled, SYSOUT will be shorted to BAT.

This system allows the step-down converter and LDOs to always have the best available source of power. This also allows the voltage converters to operate with no battery, or with a battery voltage that falls below the precondition trickle charge threshold.

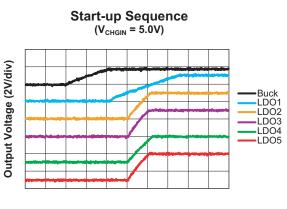

#### **Typical Power Up Sequence**

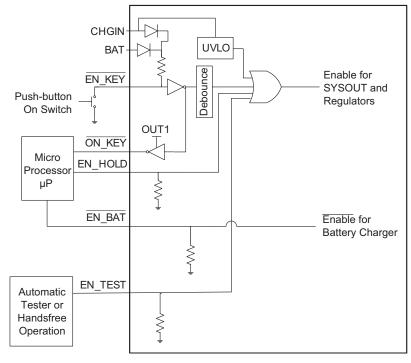

The AAT2601 supports a variety of push-button or enable/disable schemes. A typical startup and shutdown process proceeds as follows (referring to Figures 1 and 2): System startup is initiated whenever one of the following conditions occurs:

- 1) A push-button is used to assert  $EN_KEY \setminus Iow$ .

- 2) A valid supply (>CHGIN UVLO) is connected to the charger input CHGIN.

- 3) A hands free device or headset is connected, asserting EN\_TEST high.

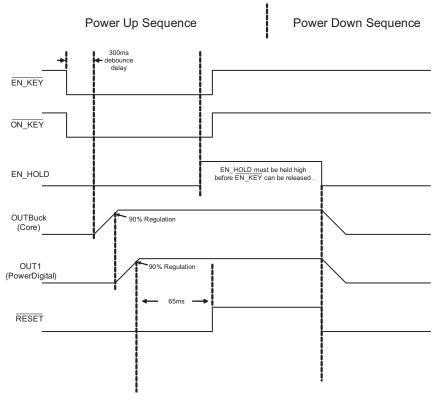

The startup sequence for the AAT2601 core (Buck and LDO1) is typically initiated by pulling the  $\overline{EN}_KEY$  pin low with a pushbutton switch, see Figure 1. The Buck (Core) is the first block to be turned on. When the output of the Buck reaches 90% of its final value, then LDO1 is enabled. When LDO1 (PowerDigital) reaches 90% of its final value, the 65ms RESET timer is initiated holding the microprocessor in reset. When the RESET pin goes High, the  $\mu$ P can begin a power up sequence. After the startup sequence has commenced, LDO2 (PowerAnalog),

LDO3 (TCXO), LDO4 (TX) and LDO5 (RX) can be enabled and disabled as desired using their independent enable pins, even while the Buck and LDO1 are still starting up. However, if they are shut down, then LDO2, LDO3, LDO4, and LDO5 cannot be enabled. The µP must pull the EN\_HOLD signal high before the EN\_KEY signal can be released by the push-button. This procedure requires that the push-button be held until the µP assumes control of EN\_HOLD, providing protection against inadvertent momentary assertions of the pushbutton. Once EN HOLD is high the startup sequence is complete. If the µP is unable to complete its power-up routine successfully before the user lets go of the push-button, the AAT2601 will automatically shut itself down. (EN\_KEY and EN\_HOLD are OR'd internally to enable the two core converters.)

Alternatively, the startup sequence is automatically started without the pushbutton switch when the CHGIN pin rises above its UVLO threshold. The system cannot be disabled until the voltage at the CHGIN pin drops below the falling UVLO threshold. Thirdly, the EN\_TEST pin can be used to startup the device for test purposes or for hands free operation such as when connecting a headset to the system.

#### **Typical Power Down Sequence**

If only the battery is connected and the voltage level is above the BAT UVLO , then the  $\overline{EN}_{KEY}$  pin can be held low in order to power down AAT2601. The user can initiate a shutdown process by pressing the push-button a second time. Upon detecting a second assertion of  $\overline{EN}_{}$  $\overline{KEY}$  (by depressing the push-button), the AAT2601 asserts  $\overline{ON}_{}$ KEY to interrupt the microprocessor which initiates an interrupt service routine that the user pressed the push-button. If  $\overline{EN}_{}$ TEST and CHGIN are both low, the microprocessor then initiates a powerdown routine, the final step of which will be to de-assert  $\overline{EN}_{}$ HOLD, disabling LDO2, LDO3, LDO4, and LDO5.

When the voltage at the CHGIN pin is above the CHGIN UVLO, the device cannot be powered down. If the voltage at the CHGIN pin is below the CHGIN UVLO, both the EN\_KEY and EN\_HOLD pins must be held low in order to power down AAT2601. If LDO2, LDO3, LDO4, and LDO5 have not been disabled individually prior to global power down, then they will be turned off simultaneously with the Buck. The outputs of LDO4 and LDO5 are internally pulled to ground with 10k during shutdown to discharge the output capacitors and ensure a fast turn-off response time.

# **AAT260I**

## **Total Power Solution for Portable Applications**

#### Figure 1: Enable Function Detailed Schematic.

Figure 2: Typical Power Up/Down Sequence.

## **Total Power Solution for Portable Applications**

## **Battery Charger**

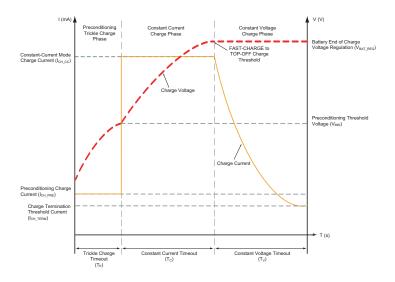

Figure 3 illustrates the entire battery charging profile which consists of three phases.

- 1. Preconditioning Current Mode (Trickle) Charge

- 2. Constant Current Mode Charge

- 3. Constant Voltage Mode Charge

#### Preconditioning Trickle Charge

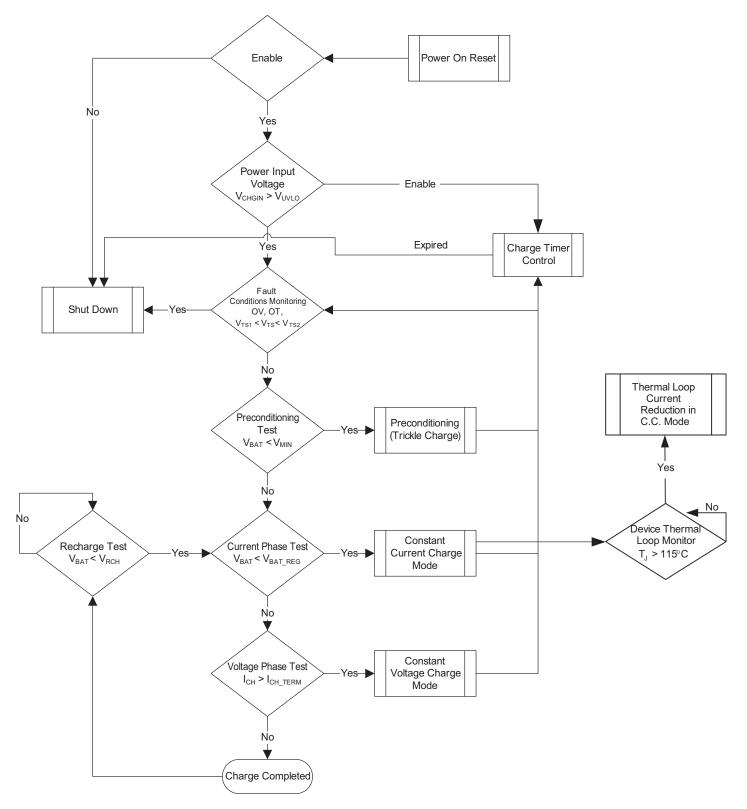

Battery charging commences only after the AAT2601 battery charger checks several conditions in order to maintain a safe charging environment. The system operation flow chart for the battery charger operation is shown in Figure 4. The input supply must be above the minimum operating voltage (UVLO) and the enable pin (ENBAT) must be low (it is internally pulled down). When the battery is connected to the BAT pin, the battery charger checks the condition of the battery and determines which charging mode to apply.

#### Preconditioning Current Mode Charge Current

If the battery voltage is below the preconditioning voltage threshold  $V_{\text{MIN}}$ , then the battery charger initiates precondition trickle charge mode and charges the battery at 12% of the programmed constant-current magnitude. For example, if the programmed current is 500mA, then the trickle charge current will be 60mA. Trickle charge is a safety precaution for a deeply discharged cell. It also reduces the power dissipation in the

internal series pass MOSFET when the input-output voltage differential is at its highest.

#### **Constant Current Mode Charge Current**

Trickle charge continues until the battery voltage reaches  $V_{\text{MIN}}$ . At this point the battery charger begins constant-current charging. The current level default for this mode is programmed using a resistor from the ISET pin to ground. Once that resistor has been selected for the default charge current, then the current can be adjusted through I<sup>2</sup>C from a range of 40% to 180% of the programmed default charge current. Programmed current can be set at a minimum of 100mA and up to a maximum of 1A. When the  $\overline{\text{ADPP}}$  signal goes high, the default I<sup>2</sup>C setting of 100% is reset. If the USE\_USB signal is high when this happens, the charge current is reset to an internally set 100mA current until the microcontroller sends another I<sup>2</sup>C signal to change the charge current. (see I<sup>2</sup>C Programming section).

#### **Constant Voltage Mode Charge**

Constant current charging will continue until the battery voltage reaches the Output Charge Voltage Regulation point  $V_{BAT\_REG}$ . When the battery voltage reaches the regulation voltage ( $V_{BAT\_REG}$ ), the battery charger will transition to constant-voltage mode.  $V_{BAT\_REG}$  is factory programmed to 4.2V (nominal). Charging in constant-voltage mode will continue until the charge current has reduced to the end of charge termination current programmed using the I<sup>2</sup>C interface (5%, 10%, 15%, or 20%).

Figure 3: Current vs. Voltage and Charger Time Profile.

## **Total Power Solution for Portable Applications**

Figure 4: System Operation Flow Chart for the Battery Charger.

#### Power Saving Mode

After the charge cycle is complete, the battery charger turns off the series pass device and automatically goes into a power saving sleep mode. During this time, the series pass device will block current in both directions to prevent the battery from discharging through the battery charger.

The battery charger will remain in sleep mode even if the charger source is disconnected. It will come out of sleep mode if either the battery terminal voltage drops below the  $V_{\text{RCH}}$  threshold, the charger EN pin is recycled, or the charging source is reconnected. In all cases, the battery charger will monitor all parameters and resume charging in the most appropriate mode.

#### **Temperature Sense (TS)**

The TS pin is available to monitor the battery temperature. Connect a 10k NTC resistor from the TS pin to ground. The TS pin outputs a  $75\mu$ A constant current into the resistor and monitors the voltage to ensure that the battery temperature does not fall outside the limits depending on the temperature coefficient of the resistor used. When the voltage goes above 2.39V or goes below 0.331V, the charging current will be suspended.

#### Charge Safety Timer (CT)

While monitoring the charge cycle, the AAT2601 utilizes a charge safety timer to help identify damaged cells and to ensure that the cell is charged safely. Operation is as follows: upon initiating a charging cycle, the AAT2601 charges the cell at 12% of the programmed maximum charge until  $V_{BAT} > 2.8V$ . If the cell voltage fails to reach the preconditioning threshold of 2.8V (typ) before the safety timer expires, the cell is assumed to be damaged and the charge cycle terminates. If the cell voltage exceeds 2.8V prior to the expiration of the timer, the charge cycle proceeds into fast charge. There are three timeout periods: 1 hour for Trickle Charge mode, 3 hours for Constant Current mode, and 3 hours for Constant Voltage mode.

The CT pin is driven by a constant current source and will provide a linear response to increases in the timing capacitor value. Thus, if the timing capacitor were to be doubled from the nominal  $0.1\mu$ F value, the time-out periods would be doubled. If the programmable watch-dog timer function is not needed, it can be disabled by terminating the CT pin to ground. The CT pin should not be left floating or unterminated, as this will cause errors

in the internal timing control circuit. The constant current provided to charge the timing capacitor is very small, and this pin is susceptible to noise and changes in capacitance value. Therefore, the timing capacitor should be physically located on the printed circuit board layout as close as possible to the CT pin. Since the accuracy of the internal timer is dominated by the capacitance value, a 10% tolerance or better ceramic capacitor is recommended. Ceramic capacitor materials, such as X7R and X5R types, are a good choice for this application.

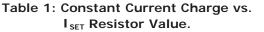

#### Programming Charge Current (ISET)

The default constant current mode charge level is user programmed with a set resistor placed between the ISET pin and ground. The accuracy of the constant charge current, as well as the preconditioning trickle charge current, is dominated by the tolerance of the set resistor. For this reason, a 1% tolerance metal film resistor is recommended for the set resistor function. The constant charge current levels from 100mA to 1A may be set by selecting the appropriate resistor value from Table 1 and Figure 5. The ISET pin current to charging current ratio is 1 to 800. It is regulated to 1.25V during constant current mode unless changed using I<sup>2</sup>C commands. It can be used as a charging current monitor, based on the equation:

$$I_{CH} = 800 \cdot \left(\frac{V_{ISET}}{R_{ISET}}\right)$$

During preconditioning charge, the ISET pin is regulated to 12% of the fast charge current  $I_{\text{SET}}$  voltage level (Figure 5), but the equation stays the same. During constant voltage charge mode, the ISET pin voltage will slew down and be directly proportional to the battery current at all times.

| Constant Charging<br>Current I <sub>CH_CC</sub> (mA) | Set Resistor<br>Value (kΩ) |

|------------------------------------------------------|----------------------------|

| 100                                                  | 10                         |

| 200                                                  | 4.99                       |

| 300                                                  | 3.32                       |

| 400                                                  | 2.49                       |

| 500                                                  | 2                          |

| 600                                                  | 1.65                       |

| 700                                                  | 1.43                       |

| 800                                                  | 1.24                       |

| 900                                                  | 1.1                        |

| 1000                                                 | 1                          |

## **Total Power Solution for Portable Applications**

#### **Reverse Battery Leakage**

The AAT2601 includes internal circuitry that eliminates the need for series blocking diodes, reducing solution size and cost as well as dropout voltage relative to conventional battery chargers. When the input supply is removed or when CHGIN goes below the AAT2601's under voltage-lockout (UVLO) voltage, or when CHGIN drops below  $V_{BAT}$ , the AAT2601 automatically reconfigures its power switches to minimize current drain from the battery.

#### Adapter Power Indicator (ADPP)

This is an open drain output which will pull low when  $V_{CHGIN} > 4.5V$ . When this happens, depending on the status of the USE\_USB pin, the charge current will be reset to the default ISET values or I<sup>2</sup>C programmed values.

#### Charge Status Output (STAT)

The AAT2601 provides battery charging status via a status pin. This pin is a buffered output with a supply level up to the LDO1 output (PowerDigital). The status pin can indicate the following conditions:

| Event Description            | STAT                         |

|------------------------------|------------------------------|

| No battery charging activity | Low (to GND)                 |

| Battery charging             | High (to V <sub>OUT1</sub> ) |

| Charging completed           | Low (to GND)                 |

Table 2: Charge Status Output (STAT).

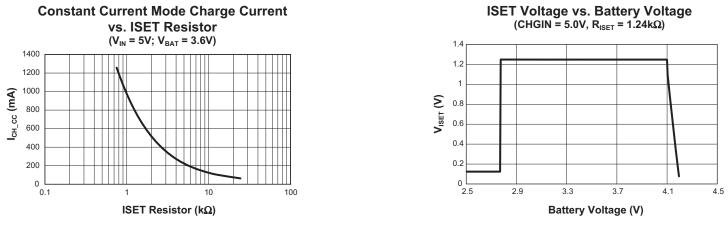

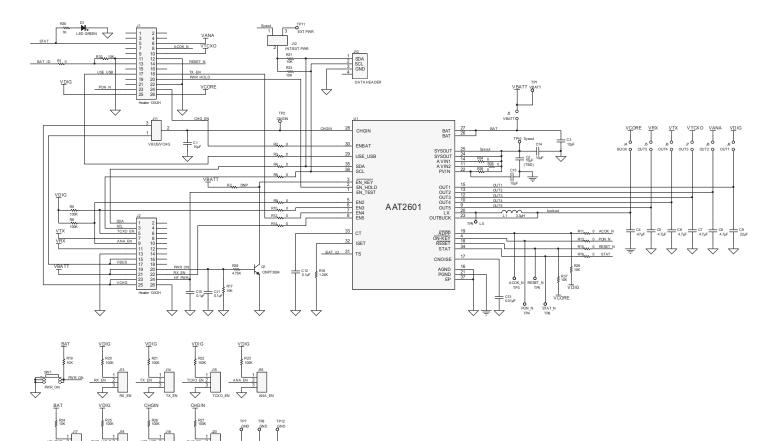

#### **CHGIN Bypass Capacitor Selection**

CHGIN is the power input for the AAT2601 battery charger. The battery charger is automatically enabled whenever a valid voltage is present on CHGIN. In most applications, CHGIN is connected to either a wall adapter or USB port. Under normal operation, the input of the charger will often be "hot-plugged" directly to a powered USB or wall adapter cable, and supply voltage ringing and overshoot may appear at the CHGIN pin. A high quality capacitor connected from CHGIN to G, placed as close as possible to the IC, is sufficient to absorb the energy. Wall-adapter powered applications provide flexibility in input capacitor selection, but the USB specification presents limitations to input capacitance selection. In order to meet both the USB 2.0 and USB OTG (On The Go) specifications while avoiding USB supply under-voltage conditions resulting from the current limit slew rate (100mA/µs) limitations of the USB bus, the CHGIN bypass capacitance value must be between 1µF and 4.7µF. Ceramic capacitors are often preferred for bypassing due to their small size and good surge current ratings, but care must be taken in applications that can encounter hot plug conditions as their very low ESR, in combination with the inductance of the cable, can create a high-Q filter that induces excessive ringing at the CHGIN pin. This ringing can couple to the output and be mistaken as loop instability, or the ringing may be large enough to damage the input itself. Although the CHGIN pin is designed for maximum robustness and an absolute

## **Total Power Solution for Portable Applications**

maximum voltage rating of +6.5V for transients, attention must be given to bypass techniques to ensure safe operation. As a result, design of the CHGIN bypass must take care to "de-Q" the filter. This can be accomplished by connecting a 1 $\Omega$  resistor in series with a ceramic capacitor (as shown in Figure 6A), or by bypassing with a tantalum or electrolytic capacitor to utilize its higher ESR to dampen the ringing (as shown in Figure 6A). For additional protection, Zener diodes with 6V clamp voltages may also be used. In any case, it is always critical to evaluate voltage transients at the CHGIN pin with an oscilloscope to ensure safe operation.

## **Thermal Considerations**

The actual maximum charging current is a function of charge adapter input voltage, the state of charge of the battery at the moment of charge, the system supply current from SYSOUT, and the ambient temperature and the thermal impedance of the package and printed circuit board. The maximum programmable current may not be achievable under all operating parameters. One issue to consider is the amount of current being sourced to the SYSOUT pin from the CHGIN LDO while the battery is being charged. The AAT2601 is offered in a TQFN55-36 package which can provide up to 4W of power dissipation when it is properly bonded to a printed circuit board and has a maximum thermal resistance of 25°C/W. Many considerations should be taken into account when designing the printed circuit board layout, as well as the placement of the charger IC package in proximity to other heat generating devices in a given application design. The ambient temperature around the charger IC will also have an effect on the thermal limits of a battery charging application. The maximum limits that can be expected for a given ambient condition can be estimated by the following discussion. First, the maximum power dissipation for a given situation should be calculated:

$$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = \frac{(\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}})}{\theta_{\mathsf{J}\mathsf{A}}}$$

Where:

$$\begin{split} P_{D(MAX)} &= Maximum \mbox{ Power Dissipation (W)} \\ \theta_{JA} &= Package \mbox{ Thermal Resistance (°C/W)} \\ T_{J(MAX)} &= Maximum \mbox{ Device Junction Temperature (°C)} \\ & [150°C] \end{split}$$

$T_A$  = Ambient Temperature (°C)

## **Total Power Solution for Portable Applications**

Next, the power dissipation for the charger can be calculated by the following equation:

$\mathsf{P}_{\mathsf{D}} = (\mathsf{V}_{\mathsf{CHGIN}} - \mathsf{V}_{\mathsf{BAT}}) \cdot \mathsf{I}_{\mathsf{CH}_{\mathsf{CC}}} + (\mathsf{V}_{\mathsf{CHGIN}} \cdot \mathsf{I}_{\mathsf{OP}}) + (\mathsf{V}_{\mathsf{CHGIN}} - \mathsf{V}_{\mathsf{SYSOUT}}) \cdot \mathsf{I}_{\mathsf{SYSOUT}}$

- +  $(V_{SYSOUT} V_{OUT1}) \cdot I_{OUT1}$  +  $(V_{SYSOUT} V_{OUT2}) \cdot I_{OUT2}$

- + (V<sub>SYSOUT</sub> V<sub>OUT3</sub>)  $\cdot$  I<sub>OUT3</sub> + (V<sub>SYSOUT</sub> V<sub>OUT4</sub>)  $\cdot$  I<sub>OUT4</sub>

- + (V<sub>SYSOUT</sub> V<sub>OUT5</sub>)  $\cdot$  I<sub>OUT5</sub>

+

$$I_{\text{OUTBUCK}^2} \cdot \left( R_{\text{DS(ON)L}} \cdot \frac{V_{\text{OUTBUCK}}}{V_{\text{SYSOUT}}} + \frac{R_{\text{DS(ON)H}} \cdot [V_{\text{SYSOUT}} - V_{\text{OUTBUCK}}]}{V_{\text{SYSOUT}}} \right)$$

Where:

$P_D$  = Total Power Dissipation by the Device  $V_{CHGIN}$  = CHGIN Input Voltage

$V_{BAT}$  = Battery Voltage at the BAT Pin

$I_{\text{CH}\_\text{CC}}$  = Constant Charge Current Programmed for the Application

$I_{OP}$  = Quiescent Current Consumed by the IC for Normal Operation [0.5mA]

$V_{\mbox{\scriptsize SYSOUT}}$  and  $I_{\mbox{\scriptsize SYSOUT}}$  = Output voltage and load current from the SYSOUT pin for the system LDOs and step-down converter [3.9V out for SYSOUT]

$R_{DS(ON)H}$  and  $R_{DS(ON)L}$  = On-resistance of step-down high and low side MOSFETs [0.8 $\Omega$  each]

$V_{\text{OUTX}}$  and  $I_{\text{OUTX}}$  = Output voltage and load currents for the LDOs and step-down converter [3V out for each LDO]

By substitution, we can derive the maximum charge current before reaching the thermal limit condition ( $T_{REG} = 100$ °C, Thermal Loop Regulation). The maximum charge current is the key factor when designing battery charger applications.

$I_{CH\_CC(MAX)} = \frac{\left(\frac{(T_{REG} - T_A)}{\theta_{JA}} - (V_{CHGIN} \cdot I_{OP})\right) - (V_{CHGIN} - V_{SYSOUT}) \cdot I_{SYSOUT})}{\theta_{JA}}$

- [(V<sub>SYSOUT</sub> - V<sub>OUT1</sub>) · I<sub>OUT1</sub>] - (V<sub>SYSOUT</sub> - V<sub>OUT2</sub>) · I<sub>OUT2</sub>

- (V<sub>SYSOUT</sub> - V<sub>OUT5</sub>) · I<sub>OUT5</sub>

$\frac{-I_{\text{OUTBUCK}}^{2} \cdot \left( R_{\text{DS(ON)L}} \cdot \frac{V_{\text{OUTBUCK}}}{V_{\text{SYSOUT}}} + \frac{R_{\text{DS(ON)H}} \cdot (V_{\text{SYSOUT}} - V_{\text{OUTBUCK}})}{V_{\text{SYSOUT}}} \right)}{V_{\text{CHGIN}} - V_{\text{BAT}}}$

In general, the worst condition is when there is the greatest voltage drop across the charger, when battery voltage is charged up to just past the preconditioning voltage threshold and the LDOs and step-down converter are sourcing full output current.

For example, if 913mA is being sourced from the 3.9V SYSOUT pin to the LDOs and Buck channels (300mA to LDO1, 100mA to LDO2-5, and 213mA to the Buck; see buck efficiency graph for 300mA output current) with a CHGIN supply of 5V, and the battery is being charged at 3.0V with 800mA charge current, then the power dissipated will be 3.32W. A reduction in the charge current (through I<sup>2</sup>C) may be necessary in addition to the reduction provided by the internal thermal loop of the charger itself.

For the above example at  $T_{\text{A}}$  = 30°C, the  $I_{\text{CH}\_\text{CC(MAX)}}$  = 546mA.

#### **Thermal Overload Protection**

The AAT2601 integrates thermal overload protection circuitry to prevent damage resulting from excessive thermal stress that may be encountered under fault conditions, for example. This circuitry disables all regulators if the AAT2601 die temperature exceeds 140°C, and prevents the regulators from being enable until the die temperature drops by 15°C (typ).

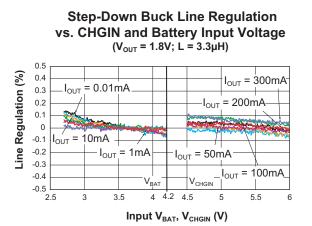

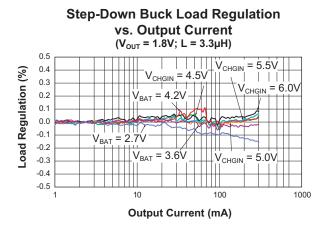

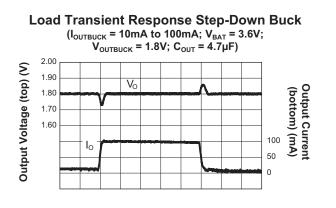

## Synchronous Step-Down Converter (Buck)

The AAT2601 contains a high performance 300mA, 1.5MHz synchronous step-down converter. The step-down converter operates to ensure high efficiency performance over all load conditions. It requires only three external power components ( $C_{IN}$ ,  $C_{OUT}$ , and L). A high DC gain error amplifier with internal compensation controls the output. It provides excellent transient response and load/line regulation. Transient response time is typically less than 20µs. The converter has soft start control to limit inrush current and transitions to 100% duty cycle at drop out.

The step-down converter input pin PVIN should be connected to the SYSOUT LDO output pin. The output voltage is internally fixed at 1.8V. Power devices are sized for 300mA current capability while maintaining over 90% efficiency at full load.

## **Total Power Solution for Portable Applications**

#### Input/Output Capacitor and Inductor

Apart from the input capacitor that is shared with the LDO inputs, only a small L-C filter is required at the output side for the step-down converter to operate properly. Typically, a  $3.3\mu$ H inductor such as the Sumida CDRH2D11NP-3R3NC and a  $4.7\mu$ F ceramic output capacitor are recommended for low output voltage ripple and small component size. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. A  $10\mu$ F ceramic input capacitor is sufficient for most applications.

#### **Control Loop**

The converter is a peak current mode step-down converter. The inner, wide bandwidth loop controls the inductor peak current. The inductor current is sensed through the P-channel MOSFET (high side) which is also used for short circuit and overload protection. A fixed slope compensation signal is added to the sensed current to maintain stability for duty cycles greater than 50%. The peak current mode loop appears as a voltage programmed current source in parallel with the output capacitor.

The output of the voltage error amplifier programs the current mode loop for the necessary peak inductor current to force a constant output voltage for all load and line conditions. The voltage feedback resistive divider is internal and the error amplifier reference voltage is 0.45V. The voltage loop has a high DC gain making for excellent DC load and line regulation. The internal voltage loop compensation is located at the output of the transconductance voltage error amplifier.

#### Soft Start

Soft start slowly increases the internal reference voltage when the input voltage or enable input is initially applied. It limits the current surge seen at the input and eliminates output voltage overshoot.

#### Current Limit and Over-Temperature Protection

For overload conditions the peak input current is limited. As load impedance decreases and the output voltage falls closer to zero, more power is dissipated internally, raising the device temperature. Thermal protection completely disables switching when internal dissipation becomes excessive, protecting the device from damage. The junction over-temperature threshold is 140°C with 15°C of hysteresis.

## Linear LDO Regulators (OUT1-5)

The advanced circuit design of the linear regulators has been specifically optimized for very fast start-up and shutdown timing. These proprietary LDOs are tailored for superior transient response characteristics. These traits are particularly important for applications which require fast power supply timing.

There are two LDO input pins, AVIN1/2, which should be connected to the SYSOUT LDO output pin. All LDO outputs are initially fixed at 3.0V. The user can program the output voltages for the LDOs to 2.8V, 2.85V, or 2.9V using  $I^2C$ .